# JVC SERVICE MANUAL

## DVD AUDIO/VIDEO PLAYER

## XV-D721BK XV-D723GD

| Area Suffix           |

|-----------------------|

| XV-D721BK             |

| J U.S.A               |

| C Canada              |

| EG Germany            |

| ES Spain              |

| EN Northern Europe    |

| EE Russian Federation |

| 1 U US Minitary       |

### Contents

| Safety Precautions 1-2            |

|-----------------------------------|

| Preventing static electricity 1-3 |

| Important for laser products 1-4  |

| Importance Admistering            |

| point on the Safety 1-5           |

| Disassembly method 1-6       |

|------------------------------|

| Adjustment method1-11        |

| Description of major ICs1-18 |

## -Safety Precautions

- 1. This design of this product contains special hardware and many circuits and components specially for safety purposes. For continued protection, no changes should be made to the original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those used in the original circuits. Services should be performed by qualified personnel only.

- 2. Alterations of the design or circuitry of the product should not be made. Any design alterations of the product should not be made. Any design alterations or additions will void the manufacturer's warranty and will further relieve the manufacture of responsibility for personal injury or property damage resulting therefrom.

- 3. Many electrical and mechanical parts in the products have special safety-related characteristics. These characteristics are often not evident from visual inspection nor can the protection afforded by them necessarily be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which have these special safety characteristics are identified in the Parts List of Service Manual. Electrical components having such features are identified by shading on the schematics and by (⚠) on the Parts List in the Service Manual. The use of a substitute replacement which does not have the same safety characteristics as the recommended replacement parts shown in the Parts List of Service Manual may create shock, fire, or other hazards.

- 4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of electric shock and fire hazard. When service is required, the original lead routing and dress should be observed, and it should be confirmed that they have been returned to normal, after re-assembling.

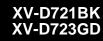

- 5. Leakage currnet check (Electrical shock hazard testing) After re-assembling the product, always perform an isolation check on the exposed metal parts of the product (antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control shafts, etc.) to be sure the product is safe to operate without danger of electrical shock. Do not use a line isolation transformer during this check.

- Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure the leakage current from each exposed metal parts of the cabinet, particularly any exposed metal part having a return path to the chassis, to a known good earth ground. Any leakage current must not exceed 0.5mA AC (r.m.s.)

- Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms per volt or more sensitivity in the following manner. Connect a  $1,500\Omega$  10W resistor paralleled by

a 0.15 $\mu$ F AC-type capacitor between an exposed metal part and a known good earth ground. Measure the AC voltage across the resistor with the

AC voltmeter. Move the resistor connection to each exposed metal part, particularly any exposed metal part having a return path to the chassis, and meaus return path to the chassis, and meausre the AC voltage across the resistor. Now, reverse the plug in the AC outlet and repeat each measurement. voltage measured Any must not exceed 0.75 V AC (r.m.s.). This corresponds to 0.5 mA AC (r.m.s.).

#### Warning

- 1. This equipment has been designed and manufactured to meet international safety standards.

- 2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

- 3. Repairs must be made in accordance with the relevant safety standards.

- 4. It is essential that safety critical components are replaced by approved parts.

- 5. If mains voltage selector is provided, check setting for local voltage.

A CAUTION Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system.

## **Preventing static electricity**

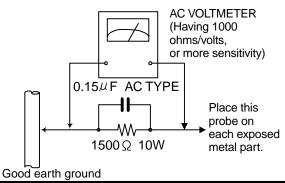

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged, can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs.

#### 1.1. Grounding to prevent damage by static electricity

Static electricity in the work area can destroy the optical pickup (laser diode) in devices such as DVD players. Be careful to use proper grounding in the area where repairs are being performed.

#### 1.1.1. Ground the workbench

1. Ground the workbench by laying conductive material (such as a conductive sheet) or an iron plate over it before placing the traverse unit (optical pickup) on it.

#### 1.1.2. Ground yourself

1. Use an anti-static wrist strap to release any static electricity built up in your body.

#### 1.1.3. Handling the optical pickup

- 1. In order to maintain quality during transport and before installation, both sides of the laser diode on the replacement optical pickup are shorted. After replacement, return the shorted parts to their original condition. (Refer to the text.)

- 2. Do not use a tester to check the condition of the laser diode in the optical pickup. The tester's internal power source can easily destroy the laser diode.

#### **1.2. Handling the traverse unit (optical pickup)**

- 1. Do not subject the traverse unit (optical pickup) to strong shocks, as it is a sensitive, complex unit.

- 2. Cut off the shorted part of the flexible cable using nippers, etc. after replacing the optical pickup. For specific details, refer to the replacement procedure in the text. Remove the anti-static pin when replacing the traverse unit. Be careful not to take too long a time when attaching it to the connector.

- 3. Handle the flexible cable carefully as it may break when subjected to strong force.

- 4. It is not possible to adjust the semi-fixed resistor that adjusts the laser power. Do not turn it

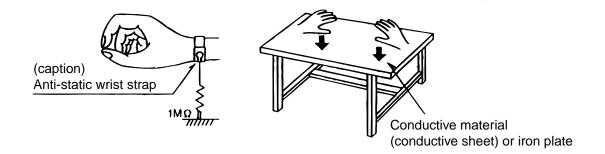

## **Important for Laser Products**

#### **1.CLASS 1 LASER PRODUCT**

- **2.DANGER :** Invisible laser radiation when open and inter lock failed or defeated. Avoid direct exposure to beam.

- **3.CAUTION :** There are no serviceable parts inside the Laser Unit. Do not disassemble the Laser Unit. Replace the complete Laser Unit if it malfunctions.

- **4.CAUTION :** The compact disc player uses invisible laserradiation and is equipped with safety switches whichprevent emission of radiation when the drawer is open and the safety interlocks have failed or are de feated. It is dangerous to defeat the safety switches.

- VARNING : Osynlig laserstrålning är denna del är öppnad och spårren är urkopplad. Betrakta ej strålen.

- VARO : Avattaessa ja suojalukitus ohitettaessa olet alttiina näkymättömälle lasersäteilylle.Älä katso säteeseen.

- **5.CAUTION :** If safety switches malfunction, the laser is able to function.

- **6.CAUTION :** Use of controls, adjustments or performance of procedures other than those specified herein may result in hazardous radiation exposure.

A CAUTION Please use enough caution not to see the beam directly or touch it in case of an adjustment or operation check.

- ADVARSEL : Usynlig laserstråling ved åbning , når sikkerhedsafbrydere er ude af funktion. Undgå udsættelse for stråling.

- ADVARSEL : Usynlig laserstråling ved åpning,når sikkerhetsbryteren er avslott. unngå utsettelse for stråling.

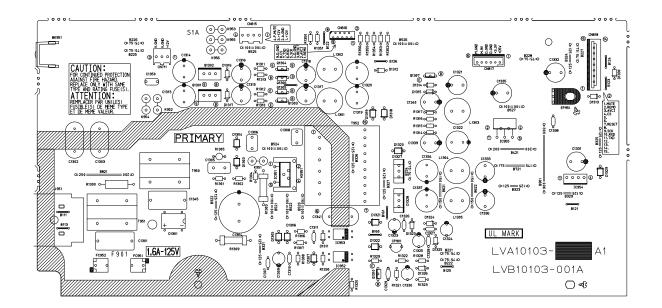

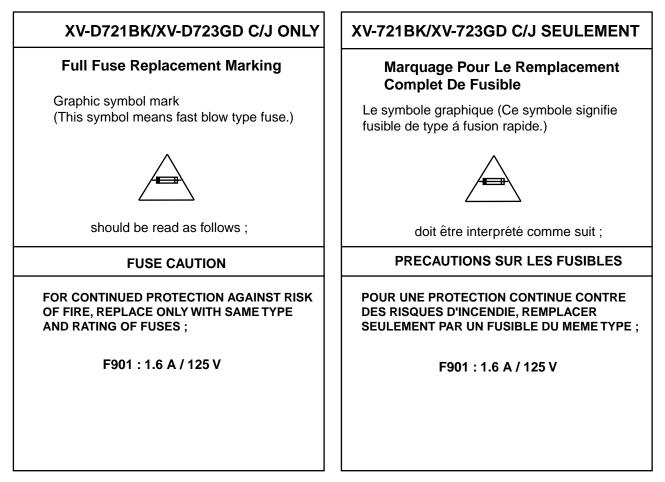

## Importance Admistering point on the Safety

Note : It's means "J" for U.S.A. market model and "C" for canada market model.

## **Disassembly method**

#### < Main body>

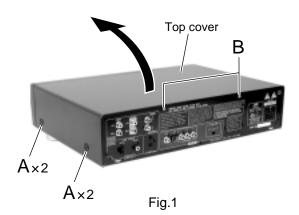

#### Removing the top cover (See Fig.1)

- 1. Remove the four screws A on each side of the body.

- 2. Remove the two screws B on the back of the body.

- 3. Remove the top cover from behind in the direction of the arrow while pulling the lower part of the sides.

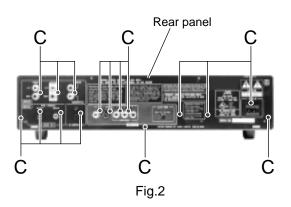

#### Removing the rear panel (See Fig.2)

- · Prior to performing the following procedure, remove the top cover.

- 1. Remove the sixteen screws C on the back of the body.

#### ■Removing the fitting (See Fig.3 to 5)

- · Prior to performing the following procedure, remove the top cover.

- ATTENTION: To remove the front panel assembly and the DVD mechanism assembly, remove the fitting in advance.

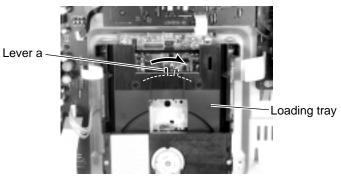

- 1. Lower the mechanism by moving the lever marked a in the direction of the arrow from the upside of the body (Refer to Fig.3).

- 2. Manually eject the loading tray toward the front.

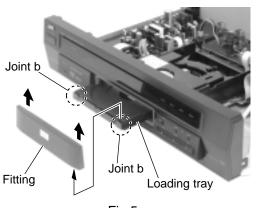

- 3. Remove the fitting from the loading tray by releasing the joints b on the both sides of the fitting.

- 4. Push and return the loading tray.

Fig.3

Fig.5

#### Removing the front panel assembly (See Fig.6 to 9)

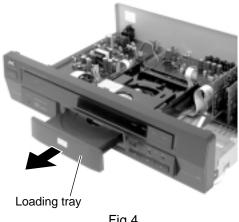

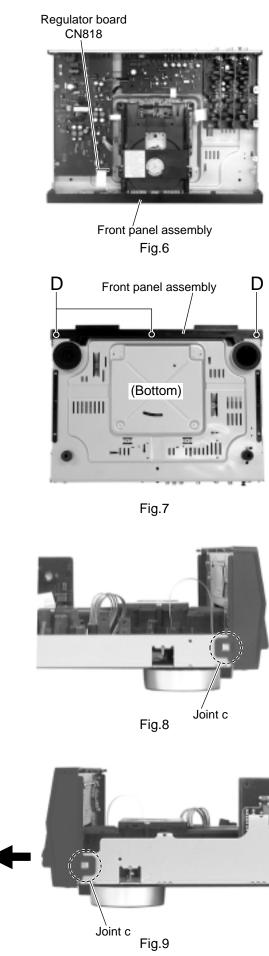

- Prior to performing the following procedure, remove the top cover and the fitting.

- 1. Disconnect the card wire from connector CN818 on the regulator board.

- 2. Turn back the body and remove the three screws D fixing the front panel assembly.

- 3. Release the two joints c on both sides of the body and remove the front panel assembly toward the front.

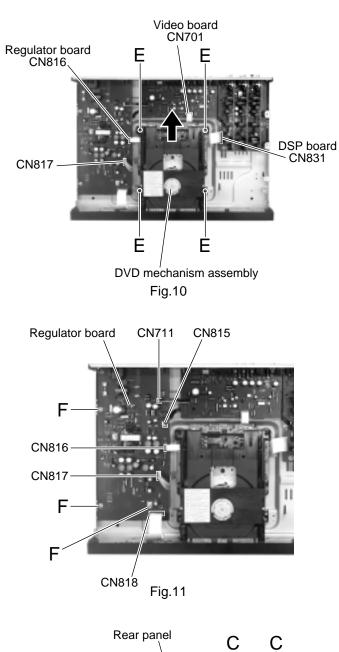

#### Removing the DVD mechanism

(See Fig.10)

- Prior to performing the following procedure, remove the top cover and the fitting.

- It is not necessary to remove the front panel assembly.

- 1. Disconnect the card wire from connector CN816 and the harness from CN817 on the regulator board.

- 2. Disconnect the card wire from connector CN701 on the video board.

- 3. Disconnect the card wire from CN831 on the DSP board.

- 4. Remove the four screws E and the DVD mechanism assembly by pulling out from the front panel assembly backward.

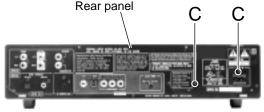

#### Removing the regulator board (See Fig.11 and 12)

- Prior to performing the following procedure, remove the top cover.

- · It is not necessary to remove the rear panel.

- 1. Disconnect the card wire from connector CN816 and CN818 and the harnesses from CN815,CN817 and CN711 on the regulator board.

- 2. Remove the three screws F attaching the regulator board.

- 3. Remove the two screws C on the rear panel.

Fig.12

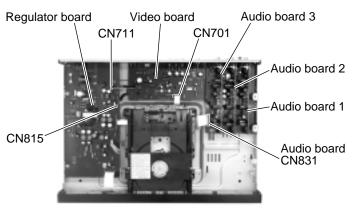

#### Removing the video board

(See Fig.13 and 14)

• Prior to performing the following procedure, remove the top cover.

Ref. : It is not necessary to remove the rear panel.

- 1. Disconnect the harnesses from the connector CN711 on the regulator board.

- 2. Disconnect the card wire from connector CN701 on the video board.

- 3. Remove the five screws C on the rear panel.

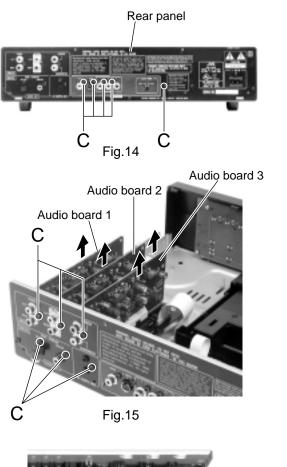

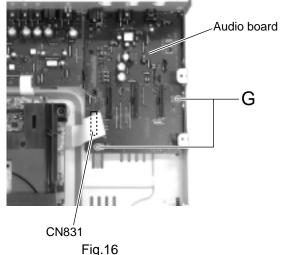

#### Removing the Audio board 1,2 and 3 / the Audio board (See Fig.13,15 and 16)

- Prior to performing the following procedure, remove the top cover and rear panel.

- 1. Remove the three screws C attaching the audio board 1,2 and 3.

- 2. Disconnect the audio board 1,2 and 3 from the audio board respectively.

- 3. Disconnect the harnesses from connector CN815 on the regulator board.

- 4. Disconnect the card wire from connector CN831 on the audio board.

- 5. Remove the two screws G attaching the audio board.

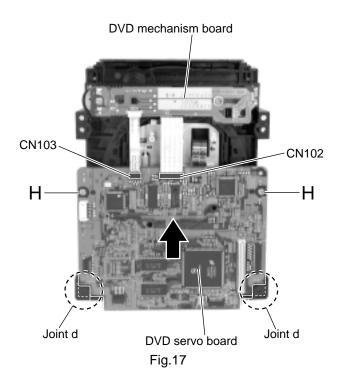

#### ■Removing the DVD servo board

(See Fig.17)

- Prior to performing the following procedure, remove the top cover and the DVD mechanism assembly.

- 1. Turn over the DVD mechanism assembly and disconnect the card wire from connector CN102 and CN103 on the DVD servo board.

- 2. Remove the two screws H attaching the DVD servo board. Move the DVD servo board in the direction of the arrow to release the two corner joints d.

#### <Front panel assembly>

- Prior to performing the following procedure, remove the top cover and the front panel assembly.

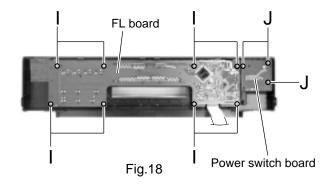

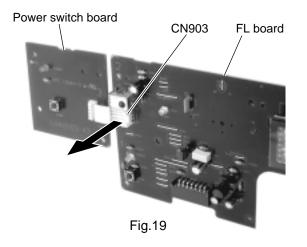

- Removing the FL board / the power switch board (See Fig.18 and 19)

- 1. Remove the eight screws I and three screws J on the back of the front panel assembly. Remove the FL board and the power switch board at the same time.

Disconnect the harness from connector CN903 on 2. the FL board.

1-10

## Adjustment method

This model has the TEST mode for simple diagnosis of the internal function. Use the TEST mode for diagnosing and checking the set as mentioned below.

#### Details of the TEST mode

The TEST mode comprises the five modes of the following.

|                                                                                                 | FL indication (*: numeral)       |

|-------------------------------------------------------------------------------------------------|----------------------------------|

| 1.DVD AUDIO copyright protection key serial indication                                          | ******************************** |

| Indicates the content of the DVD AUDIO copyright at shipment. Use this mode for checking it.    |                                  |

| 2. Microcomputer's version number indication                                                    | ** _** _**                       |

| Indicates the initial version number of the microcomputer at shipment. Use this mode for checki | ing it.                          |

| 3.Servo signal system check mode                                                                | CHECK                            |

| Use this mode for checking the laser pickup status.                                             |                                  |

| 4.Indication check mode The                                                                     | FL and LED's go on in full.      |

| The LED's and FL of the set go on in full. Use this mode for checking indications.              |                                  |

| 5.Microcomputer software upgrading mode                                                         | UPGRADE                          |

| Use this mode for upgrading the microcomputer software.                                         |                                  |

#### How to set the TEST mode

1. While pressing the STOP key and PLAY key of the set together, plug in the power cord.

\*Continue to pressing both the STOP key and PLAY key until reading of disk data completes (until the "NOW READING" message changes into a DVD logo).

2."TEST \*" message appears on the FL. (\* In the part of the sign, the sign is different according to the destination.)

3. The five modes of the TEST mode change one after another each time the DISPLAY OFF key of the set is pressed.

4. To recover the usual operation mode, turn off the set by pressing the POWER ON/OFF key.

#### How to check the laser pickup

Since the laser pickup of the set is easily affected by static electricity, heat, etc., it may be damaged depending on use condition. If the set shows such a symptom as it fails in reading disk data, check the laser pickup as follows.

\* Checking laser current

1.Enter the set into the "servo signal system check mode" of the TEST mode.

2.Press the SKIP | << key of the set.

The laser is turned on and the LAS \*\*\*\* message appears on the FL display. \*\*\*\* in the message indicates the current in code. For knowing the actual laser current, read the first two figures (omitting the last two figures) and convert the number into the current (mA) referring to the following conversion table, because the FL indication is a hexadecimal number. Since the FL indication varies because of self-heating of the set, read the indication value about 20 seconds after the set was turned on. If the indicated value is the OK level (see the conversion table), the laser is judged to be normal in the initial status by this simple checking method.

3. Press the STOP key to set back the check mode to the initial status.

| FL indication | Current (mA) | Judgment | FL indication | Current (mA) | Judgment | FL indication | Current (mA) | Judgment |  |

|---------------|--------------|----------|---------------|--------------|----------|---------------|--------------|----------|--|

| 38            | 1.2          | OK       | 04            | 35.6         | OK       | DO            | 70.0         | NG       |  |

| 34            | 3.9          | OK       | 00            | 38.3         | OK       | CC            | 72. 7        | NG       |  |

| 30            | 6.5          | OK       | FC            | 40.9         | OK       | C8            | 75.3         | NG       |  |

| 20            | 9.1          | OK       | F8            | 43.6         | OK       | C4            | 78.0         | NG       |  |

| 28            | 11.8         | OK       | F4            | 46.2         | OK       | CO            | 80.0         | NG       |  |

| 24            | 14.4         | OK       | F0            | 48.8         | OK       | BC            | 83. 2        | NG       |  |

| 20            | 17.1         | OK       | EC            | 51.5         | OK       | B8            | 86.0         | NG       |  |

| 10            | 19.7         | OK       | E8            | 54.1         | OK       | B4            | 88.5         | NG       |  |

| 18            | 22. 4        | OK       | E4            | 56.8         | OK       | B0            | 91.2         | NG       |  |

| 14            | 25.0         | OK       | E0            | 59.4         | OK       | AC            | 93.8         | NG       |  |

| 10            | 27.7         | OK       | DC            | 62.1         | NG       | A8            | 96.5         | NG       |  |

| 00            | 30.3         | OK       | D8            | 64. 7        | NG       | A4            | 99.1         | NG       |  |

| 08            | 33.0         | OK       | D4            | 67.4         | NG       |               |              |          |  |

#### Laser current conversion table

#### \* Automatic adjustment/Jitter value indication

1.Enter the set into the "servo signal system check mode" of the TEST mode.

2.Open the tray with the OPEN key of the set. Set the TEST disk VT-501 on the tray and put back the tray with the CLOSE key. Then, press the PAUSE key.

The TEST disk starts rotation to execute automatic adjustment. If the set is in the normal condition, the "CHECK OK" message appears. If there is something abnormal in the adjustment values, an error message appears and it mostly comes from a failure in the servo system (including the mechanism and pickup). In such the event, refer to the check points by errors.

When using the TEST disk VT-501, carefully check to see if there is neither damage nor dirt on the read surface of the disk beforehand.

3. Press the STOP key to return the check mode to the initial status.

4.After the automatic adjustment with the TEST disk completes, press the PLAY key.

The disk starts rotation and a jitter value (signal read precision in percentage) appears on the FL display (JIT 0\*\*\*). If the indication value (in \*\*\* places) is 110 (11 %) or less, it can be judged by this simple checking method that the signal read precision of the set is satisfactory.

Before using the TEST disk VT-501, carefully check it if there is neither damage nor dirt on the read surface. 5. Press the STOP key to return the mode to the initial status.

#### Upgrading microcomputer software

The internally incorporated microcomputer software of this set can be revised in part for the reason that the set is designed to conform to new standards and to be capable of playing disks to be put on the market by other manufacturers. To upgrade the internal microcomputer software, use the upgrade disk and follow the procedure mentioned below.

\* How to upgrade the microcomputer software

- 1.Set the upgrade disk in the set and enter it into the TEST mode.

- 2.After confirming that the set completes reading of the upgrade disk data while looking at the indication on the monitor screen, change the TEST mode to the microcomputer software upgrading mode and then press the PLAY key.

- 3. The set completes writing of the upgrade disk data approximately 1 minute later and it is automatically reset by the self-resetting function. Then the set again reads the upgrade disk and stops automatically.

- 4. Take the upgrade disk out of the set and turn it off with the POWER ON/OFF key.

- 5. Again enter the set into the TEST mode, and press the SKIP **I** key and then the PAUSE key.

- 6.Make sure that the DVD AUDIO indicator goes on a few seconds after the above-mentioned operation, check the version number of the microcomputer software in the microcomputer software version number indication mode.

\*Carefully carry out the above procedure. If data write is interrupted in the middle of course by power failure or careless shutdown operation, not only the data of the internal software may be damaged but the set may fail in resetting. The version number of the internal microcomputer software is shown as follows.

FL indication: \*\* \*\*

[IC901] [IC401] [IC508/IC509] V Symbol number of microcomputer IC

#### Initializing the set

Initialization of the set returns it to the initial status at shipment. Be sure to initialize the set after repair service.

\* How to initialize the set

1.Enter the set into the TEST mode and press the SKIP ► key first and the PAUSE key second. 2.Make sure that the DVD AUDIO indicator goes on a few seconds later.

#### DVD AUDIO copyright protection

To protect the DVD AUDIO copyright from infringement, a number proper to each DVD AUDIO set called a device key is assigned to each set. If a proper device key is not set for a set, it fails in playing a copyrighted disk.

The management number of the device key of a set can be checked by the DVD AUDIO copyright protection key serial indication in the TEST mode. If the "???...." message appears in this check mode, the set has a failure in the device key. If it occurs, inquire at the Service Section of the Audio and Communication Division, JVC.

#### Check points for each error

(1) Spindle start error

\*Defective spindle motor Are there 10ohms resistance between each pin of CN102 "1~4"? (The power supply is turned off and measured.)

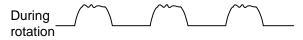

\*Hall element: Is sine wave output between CN102 "10" and "11", between "12" and "13", and between "14" and "15" during rotation?

In either case, replace the mechanical unit.

\*Defective spindle driver (IC251) Is a driving wave output from CN102 "1~4" ?

Is IC251 "9" at "H" level (START)? Servo IC --- Is control signal sent to the motor driver ?

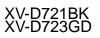

IC201 "95": Duty is 50% during stop, but varies during rotation (greatly varies at start). --- If not sent, pattern or servo IC (IC201) is defective.

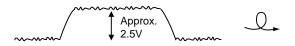

R259 : approx 2.5V during stop, but varies during rotation (greatly varies at start). --- of not sent, pattern or servo IC (IC201) is defective.

Is FG input to servo IC ? Observe FG wave from IC201 "89". --- If not output, pattern, IC251 or IC201 is defective.

(2) Disc Detection, Distinction error (no disc, no REFNV)

\* Laser is defective.

- \* Front End Processor is defective (IC101).

- \* APC circuit is defective. --- Q101.

- \* Pattern is defective. --- Lines for CN101 "15" and "17".

Lines for between IC201 "2" and IC101 "2"(LDONA),

between IC201 "3" and IC101 "1" (LDONB).

\* Servo IC is defective (IC201).

- \* Is signal sent to IC201(servo)"71" AS2 ?

- \* IC101 --- For signal from IC101 to IC301, is signal output from IC101 "88" (RFAS1) and IC101 "69" REENV ?

#### (3) Traverse movement NG

- \* For automatic adjustment, traverse movement occurs only when the position is changed to retry judging the disc type after the 1st judgment resulted in an error. Therefore, traverse movement rarely occurs because, in most cases, disc judgment at the current position (1st time judgment) is executed successfully. (Of course, NG rarely occurs in this step.)

- Note: 1st time judgment of disc type resulted in NG. --- The re-judgment of disc type may not be successful. Therefore, after removing the cause of traverse movement, re-execute automatic adjustment and confirm that no problem exists.

- \* Check point

- a) During stop

Whether 50% duty pulse is output to R273 Whether between R274 and C271 is at approx. 2.5VDC Offset voltage between CN102 "1" and "2" (scores mV if exists)

When tray is opened or closed

Check by oscilloscope whether a rectangular wave signal is output from CN102 "1" or "2".

If checking a) or b) resulted in NG, IC201 maybe defective.

#### (4) Focus ON NG

- \* Is FE output ? --- Pattern, IC101

- \* Is FCDRV signal sent ? (R286) --- Pattern, IC301

- \* Is driving voltage sent ?

CN101 "1", "3" --- If NG, pattern, driver, mechanical unit (with the power turned off, measure the resistance between CN101 "20" and "21").

- \* Does CN101 "8" become "H" and is the focus drawing in done?

- --- Mechanical unit (laser power too low), IC101(defective gain)

- --- Moreover, It is thought that abnormality is found in the disk.

- \* Mechanical unit is defective.

#### (5) Tracking ON NG

- \* When the tracking loop cannot be drawn in, IC201 "58" (/TRON) does not become "L".

- \* Mechanical unit is defective.

Because the undermentioned adjustment value is abnormal, it is not possible to draw in normally.

\* Periphery of driver (IC271)

Constant or IC it self is defective.

(When passing without becoming abnormal while adjusting the following.)

\* Servo IC (IC201)

When improperly adjusted due to defective IC.

[Focus position rough adjustment] [Phase difference cancellation rough adjustment] [Tracking balance adjustment]

- (6) Spindle CLV NG

- \* When the spindle cannot be shifted to CLV Servo, does not become "H" between IC201 "18" and IC301"88".

- \* IC201 Is signal output from IC101 "87" (RFOP)?

- \* IC201 Is signal output from IC201 "60" to "64" (binary-coded clock and data)?

- \* IC201 Is "58" (/TRON) at "L" level ?

- \* IC301 "74" to "76" --- Is signal output to IC201 "24", "25", "28" (In case of only CD).

- (Serial communication of rotation information)

- \* Spindle motor driver is defective.

Even when one of the three phases is defective, item (1) may be passed.

--- Check the second item in (1) above.

- \* C260 to C263 Defective soldering

- If noise eliminating capacitors are not properly soldered, noise may ride on the waveform.

- \* Besides, the undermentioned cause is though though specific of the cause is difficult because various factors are thought.

Mechanism is defective.(jitter) IC101, IC201.

(7) Address read NG

\* Besides, the undermentioned cause is thought though specific of the cause is difficult because various factors are thought.

Mechanism is defective. (jitter) IC201, IC301, IC401. The disc is dirty or the wound has adhered.

- (8) Between layers jump NG (double-layer disc only)

- \* When the focus flight is generated when jumps between layers. Because all adjustments for L1 layer must be successful, this error may rarely be due to a circuit defect.

- \* Crosstalk might occur from tracking to focus system. (See (11)) --- Replace the mechanical unit.

- \* Driver surroundings.

- \* Defect of constant and IC.

- \* For double-layer discs, after checking CLV on layer L1, jumps to layer L0 after mode changes to FG. Then tracking is turned off, and adjustments are executed from the focus position coarse adjustment in order.

- \* When the jump between layers is done on the single-layer disk, the disk distinction error is thought.

- --- The laser power is low (RF level is confirmed by IC101"87" (RFOP)).

- --- AS1, AS2, REFNV Is the signal sent to between IC101 and IC201 ?

- (9) Neither picture nor sound is output

- \* Cannot search

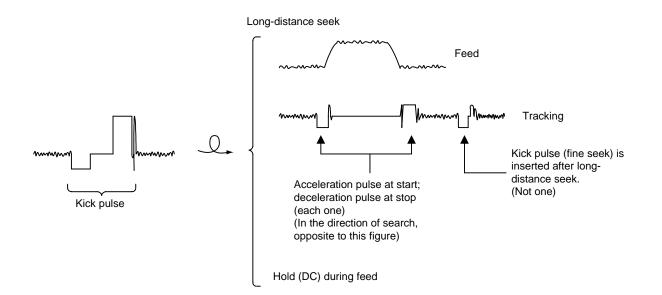

- a) Can the feed system be driven?

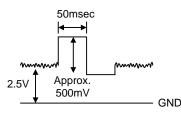

- Check the waveform of TRSDRV signal (R273). --- Waveform between R274 and C271.

Search results in a change of duty (three values with 2.5V at the center) (The figure is exaggerated.)

Check the waveform of CN101 "1" and "2". --- After the driver (IC271)

For short-distance search, the waveform becomes roundish, not trapezoidal, and voltage is low.

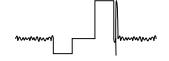

b) Is kick available?

Check the TRDRV signal waveform from R289.

Check the waveform of CN101 "2" and "4" --- After the driver (IC271) Although differs in amplitude and DC offset, the waveform is similar to that of R289

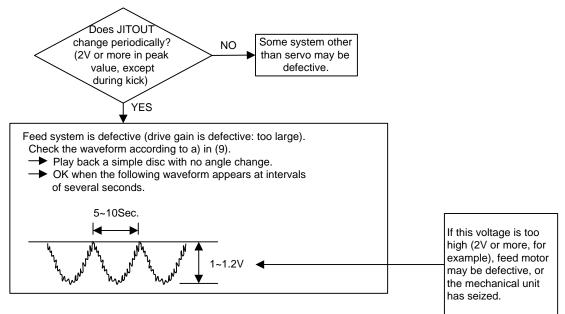

(10) Picture is distorted or abnormal sound occurs at intervals of several seconds.

- (11) Others (unusual events experienced to date)

- \* Problem occurs with double-layer discs although no problem occurs with single-layer DVD. (Error occurs, or search becomes unstable and takes longer.)

- Crosstalk might occur from tracking to focus system.

- --- When FE was observed during search (skip, etc.), it was found that a wave resembling TE with an amplitude of 200mVp-p was riding on FE.

- --- Mechanical unit was replaced.

- \* Error frequently occurred in the outer part of discs although no error occurred in the inner part. --- Mechanical unit was replaced because tilt seemed to be defective.

- (12) CD During normal playback operation

| a) Is TOC reading normal?<br>Displays total time<br>for CD-DA.<br>Shifts to double-speed<br>mode for V-CD. | NO | Please refer to "Servo Volume" flow.                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b)Playback possible?                                                                                       | NO | <ul> <li>*: is displayed during FL serch.<br/>According to [*Cannot serch ] for DVD(9), check the feed<br/>and tracking systems.</li> <li>*No sound is output although the time is displayed.(CA-DA)</li> <li>*DAC, etc, other than servo.</li> <li>*The passage of time is not stable, or picture is abnormal.(V-CD)</li> <li>*The wound of the disc and dirt are confirmed.</li> </ul> |

#### (13) Others

V-CD : Frequent occurrence of error in inside and outer. (Even the disk without the wound : when generated.)

Waveform observation

- --- Is the oscillation frequency of about 700~900Hz output?

- (Borrow a pertinent disk for the complaint for the combination with the disk.)

- --- Exchanges mechanism for the mechanism resonance.

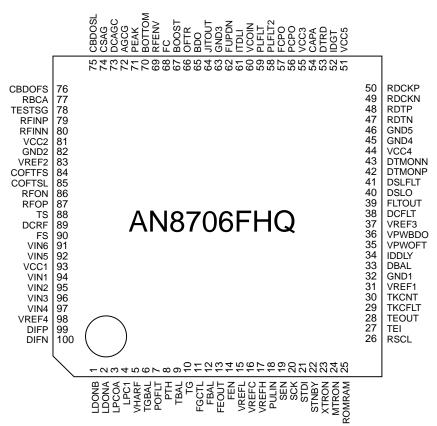

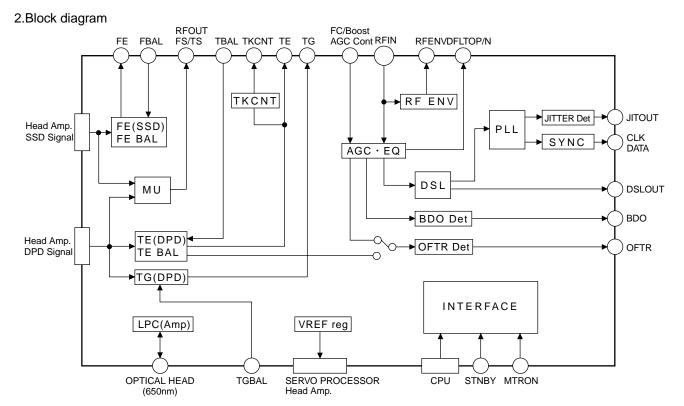

## ■ AN8706FHQ (IC101) : Front end processor

1.Pin layout

|         |        |          | AN8706FHQ (1/2)                                                              |  |  |  |  |

|---------|--------|----------|------------------------------------------------------------------------------|--|--|--|--|

| Pin No. | Symbol | I/O      | Functions                                                                    |  |  |  |  |

| 1       | LDONB  | Ι        | Laser ON (CD Head) terminal                                                  |  |  |  |  |

| 2       | LDONA  | Ι        | Laser ON (DVD Head) terminal                                                 |  |  |  |  |

| 3       | LPCOA  | 0        | Laser drive output terminal                                                  |  |  |  |  |

| 4       | LPC1   | Ι        | Laser PIN input terminal                                                     |  |  |  |  |

| 5       | VHARF  | 0        | VHALF voltage output terminal                                                |  |  |  |  |

| 6       | TGBAL  | Ι        | Tangential phase balance control terminal                                    |  |  |  |  |

| 7       | POFLT  | 0        | Track detection Threshold value level terminal                               |  |  |  |  |

| 8       | PTH    | Ι        | Track detection Threshold value level terminal                               |  |  |  |  |

| 9       | TBAL   | Ι        | Tracking balance control terminal                                            |  |  |  |  |

| 10      | TG     | 0        | Tangential phase error signal output terminal                                |  |  |  |  |

| 11      | FGCTL  | Ι        | Focus amplifier Gain control terminal                                        |  |  |  |  |

| 12      | FBAL   | Ι        | Focus balance control terminal                                               |  |  |  |  |

| 13      | FEOUT  | 0        | Focus error signal output terminal                                           |  |  |  |  |

| 14      | FEN    | Ι        | Focus error output amplifier reversing input terminal                        |  |  |  |  |

| 15      | VREFL  | 0        | VREFL voltage output terminal                                                |  |  |  |  |

| 16      | VREFC  | 0        | VREFC voltage output terminal                                                |  |  |  |  |

| 17      | VREFH  | 0        | VREFH voltage output terminal                                                |  |  |  |  |

| 18      | PULIN  | -        | DSL,PLL drawing mode switch terminal                                         |  |  |  |  |

| 19      | SEN    | I        | SEN(Cereal data input terminal)                                              |  |  |  |  |

| 20      | SCK    | ·        | SCK(Cereal data input terminal)                                              |  |  |  |  |

| 21      | STDI   | ·        | STDI(Cereal data input terminal)                                             |  |  |  |  |

| 22      | STNBY  |          | Standby mode control terminal                                                |  |  |  |  |

| 23      | XTRON  | ·<br>    | Tracking OFF holding input terminal                                          |  |  |  |  |

| 24      | MTRON  |          | Monitor output ON/OFF switch terminal                                        |  |  |  |  |

| 25      | ROMRAM |          | ROM • RAM switch terminal                                                    |  |  |  |  |

| 26      | RSCL   | 0        | Standard current source terminal                                             |  |  |  |  |

| 27      | TEI    | <u> </u> | Tracking error output Amp reversing input terminal                           |  |  |  |  |

| 28      | TEOUT  | 0        | Tracking error signal output terminal                                        |  |  |  |  |

| 29      | TKCFLT | 0        | Track count detection filter terminal                                        |  |  |  |  |

| 30      | TKCNT  | 0        | Track count output terminal                                                  |  |  |  |  |

| 31      | VREF1  | 0        | VREF1 voltage output terminal                                                |  |  |  |  |

| 32      | GND1   | 0        | Earth terminal 1                                                             |  |  |  |  |

| 33      | DBAL   | 1        | Data slice offset adjustment terminal                                        |  |  |  |  |

| 34      | IDDLY  |          | Data slice delay adjustment terminal                                         |  |  |  |  |

| 35      | VPWOFT |          | OFTR detection level setting terminal                                        |  |  |  |  |

| 36      | VPWBDO | 1        | BDO detection level setting terminal                                         |  |  |  |  |

| 37      |        |          |                                                                              |  |  |  |  |

|         | VREF3  | 0        | VREF3 voltage output terminal                                                |  |  |  |  |

| 38      | DCFLT  | 0        | Capacity connection terminal for data slice input filter                     |  |  |  |  |

| 39      | FLTOUT | 0        | Filter amplifier output terminal                                             |  |  |  |  |

| 40      | DSLO   | 0        | Data slice single data output terminal                                       |  |  |  |  |

| 41      | DSLFLT | 0        | Constant filter terminal when data is sliceddelly                            |  |  |  |  |

| 42      | DTMONP | 0        | PLL differential motion 2 making to value edge signal moniter output (+)     |  |  |  |  |

| 43      | DTMONN | 0        | PLL differential motion 2 making to value edge signal moniter output (-)     |  |  |  |  |

| 44      | VCC4   |          | Power terminal 4 (5V)                                                        |  |  |  |  |

| 45      | GND4   | 0        | Earth terminal 4                                                             |  |  |  |  |

| 46      | GND5   | 0        | Earth terminal 5                                                             |  |  |  |  |

| 47      | RDTN   | 0        | PLL differential motion making to synchronization RF signal reversing output |  |  |  |  |

| 48      | RDTP   | 0        | PLL differential motion making to synchronization RF signal rotation output  |  |  |  |  |

| 49      | RDCKN  | 0        | PLL differential motion making synchronization clock reversing output        |  |  |  |  |

| 50      | RDCKP  | 0        | PLL differential motion making synchronization clock rotation output         |  |  |  |  |

| Pin No.  | Symbol           | I/O | Functions                                                                                |  |  |  |  |  |

|----------|------------------|-----|------------------------------------------------------------------------------------------|--|--|--|--|--|

| 51       | VCC5             | 1   | Power terminal 5 (3.3V)                                                                  |  |  |  |  |  |

| 52       | IDGT             | I   | Data slice part address part gate signal input terminal (For RAM)                        |  |  |  |  |  |

| 53       | DTRD             | i   | Data slice data read signal input terminal(For RAM)                                      |  |  |  |  |  |

| 54       | CAPA             | 1   | Data slice CAPA(Address)signal input terminal (For RAM)                                  |  |  |  |  |  |

| 55       | VCC3             | i   | Power terminal 3 (5V)                                                                    |  |  |  |  |  |

| 56       | PCPO             | 0   | PLL phase gain set terminal                                                              |  |  |  |  |  |

| 57       | FCPO             | 0   | PLL frequency gain set terminal                                                          |  |  |  |  |  |

| 58       | PLFLT2           | 0   | PLL low region filter terminal                                                           |  |  |  |  |  |

| 59       | PLFLT            | 0   | PLL high region filter terminal                                                          |  |  |  |  |  |

| 60       | VCOIN            | I   | PLL VCO input terminal                                                                   |  |  |  |  |  |

| 61       | ITDLI            | 0   | PLL jitter free current ripple removal filter terminal                                   |  |  |  |  |  |

| 62       | FUPDN            | I   | PLL frequency control input terminal                                                     |  |  |  |  |  |

| 63       | GND3             | 0   | Earth terminal 3                                                                         |  |  |  |  |  |

| 64       | JITOUT           | 0   | Detection signal output of jitter                                                        |  |  |  |  |  |

| 65       | BDO              | 0   | BDO output terminal                                                                      |  |  |  |  |  |

| 66       | OFTR             | 0   | OFTR output terminal                                                                     |  |  |  |  |  |

| 67       | BOOST            |     | Booth control terminal for filter                                                        |  |  |  |  |  |

| 68       | FC               |     | FC control terminal for filter                                                           |  |  |  |  |  |

| 69       | RFENV            | 0   | RF enve output terminal                                                                  |  |  |  |  |  |

| 70       | BOTTOM           | 0   | Bottom enve detection filter terminal                                                    |  |  |  |  |  |

| 70       | PEAK             | 0   | Peak enve detection filter terminal                                                      |  |  |  |  |  |

| 71       | AGCG             | 0   |                                                                                          |  |  |  |  |  |

| 72       | DCAGC            | 0   | AGC amplifier gain control terminal AGC amp filter terminal                              |  |  |  |  |  |

| 73       | CSAG             | 0   | Sag cancellation circuit filter terminal                                                 |  |  |  |  |  |

|          |                  | 0   |                                                                                          |  |  |  |  |  |

| 75<br>76 | CBDOSL<br>CBDOFS | 0   | BDO detection capacitor terminal                                                         |  |  |  |  |  |

|          | RBCA             |     | BDO detection capacitor terminal                                                         |  |  |  |  |  |

| 77<br>78 | TESTSG           | 0   | BCA detection level setting terminal<br>TEST signal input terminal                       |  |  |  |  |  |

| 78       | RFINP            |     | RF signal positive moving input terminal                                                 |  |  |  |  |  |

| 80       | RFINE            |     | RF signal reversing input terminal                                                       |  |  |  |  |  |

| 81       | VCC2             |     | Power terminal 2 (5V)                                                                    |  |  |  |  |  |

| 82       | GND2             | 0   | Earth terminal 2                                                                         |  |  |  |  |  |

|          |                  | -   | VREF2 voltage output terminal                                                            |  |  |  |  |  |

| 83       | VREF2            | 0   |                                                                                          |  |  |  |  |  |

| 84       | COFTE            | 0   | OFTR detection capacitor terminal                                                        |  |  |  |  |  |

| 85<br>86 | COFTFL<br>RFON   | 0   | OFTR detection capacitor terminal<br>RF signal output terminal P                         |  |  |  |  |  |

| -        |                  | 0   |                                                                                          |  |  |  |  |  |

| 87<br>88 | RFOP             | 0   | RF signal output terminal N<br>All addition amplifier (DVD) output terminal              |  |  |  |  |  |

| 88       |                  | 0   |                                                                                          |  |  |  |  |  |

| 89<br>00 | DCRF<br>FS       | 0   | All addition amplifier capacitor terminal<br>All addition amplifier (CD) output terminal |  |  |  |  |  |

| 90       |                  | -   |                                                                                          |  |  |  |  |  |

| 91       | VIN6             |     | Focus input of external division into two terminal                                       |  |  |  |  |  |

| 92<br>93 | VIN5             |     | Focus input of external division into two terminal                                       |  |  |  |  |  |

|          | VCC1             |     | Power terminal 1 (5V)                                                                    |  |  |  |  |  |

| 94       | VIN1             |     | External division into four (DVD/CD) RF input terminal 1                                 |  |  |  |  |  |

| 95<br>06 | VIN2             |     | External division into four (DVD/CD) RF input terminal 2                                 |  |  |  |  |  |

| 96       | VIN3             |     | External division into four (DVD/CD) RF input terminal 3                                 |  |  |  |  |  |

| 97       | VIN4             |     | External division into four (DVD/CD) RF input terminal 4                                 |  |  |  |  |  |

| 98       | VREF4            | 0   | VREF4 voltage output terminal                                                            |  |  |  |  |  |

| 99       | DIFP             | 0   | RF signal (RAM) output terminal P                                                        |  |  |  |  |  |

| 100      | DIFN             | 0   | RF signal (RAM) output terminal N                                                        |  |  |  |  |  |

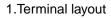

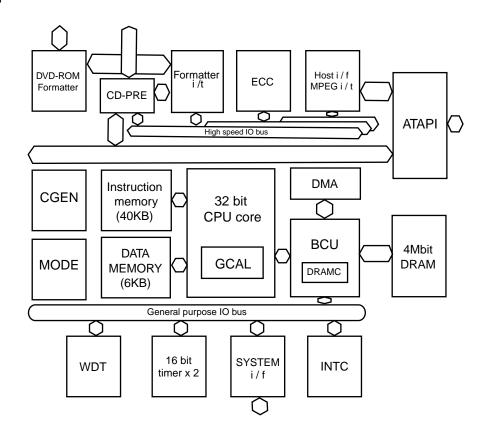

#### MN103007BGA (IC301) : Optical disc controller

2.Block diagram

#### 3.Function

MN103007BGA(1/2)

|         |          | -        |                                |         |           |     | MN103007BGA(1/2)               |

|---------|----------|----------|--------------------------------|---------|-----------|-----|--------------------------------|

| Pin NO. | Symbol   | I/O      | Function                       | Pin NO. | Symbol    | I/O | Function                       |

| 1       | HDD15    | I/O      | ATAPI data                     | 48      | CPUADR8   | Ι   | System control address         |

| 2       | HDD0     | I/O      | ATAPI data                     | 49      | CPUADR7   | Ι   | System control address         |

| 3       | HDD14    | I/O      | ATAPI data                     | 50      | CPUADR6   | Ι   | System control address         |

| 4       | 5VDD     |          |                                | 51      | CPUADR5   | Ι   | System control address         |

| 5       | HDD1     | I/O      | ATAPI data                     | 52      | CPUADR4   | Ι   | System control address         |

| 6       | HDD13    | I/O      | ATAPI data                     | 53      | CPUADR3   | Ι   | System control address         |

| 7       | HDD2     | I/O      | ATAPI data                     | 54      | CPUADR2   | Ι   | System control address         |

| 8       | VSS      |          |                                | 55      | CPUADR1   | Ι   | System control address         |

| 9       | HDD12    | I/O      | ATAPI data                     | 56      | VSS       |     | GND                            |

| 10      | VDD      |          |                                | 57      | CPUADR0   | Ι   | System control address         |

| 11      | HDD3     | I/O      | ATAPI data                     | 58      | NCS       | Ι   | System control chip selection  |

| 12      | HDD11    | I/O      | ATAPI data                     | 59      | NWR       | 1   | System control wright          |

| 13      | HDD4     | I/O      | ATAPI data                     | 60      | NRD       |     | System control lead            |

| 14      | HDD10    | 1/O      | ATAPI data                     | 61      | VDD       |     | Apply 3V                       |

| 15      | 5VDD     |          |                                | 62      | CPUDT7    |     | System control data            |

| 16      | HDD5     | I/O      | ATAPI data                     | 63      | CPUDT6    |     | System control data            |

| 17      | HDD9     | 1/0      | ATAPI data                     | 64      | PVPPDRAM  | 0   | C=10000PF is connected         |

| 18      | VSS      | 1/0      |                                |         |           | Ŭ   | between VSS                    |

| 19      | HDD6     | I/O      | ATAPI data                     | 65      | PTESTDRAM | -   | VSS connected                  |

| 20      | HDD8     | 1/O      | ATAPI data                     | 66      | OVDDDRAM  | -   | VOO connected                  |

| 20      | HDD7     | 1/O      | ATAPI data                     | 67      | PVSSDRAM  |     |                                |

| 22      | 5VDD     | 1/0      |                                | 68      | CPUDT5    |     | System control data            |

| 22      | NRESET   | 1        | ATAPI reset                    | 69      | CPUDT4    |     | System control data            |

| 23      | MASTER   | 1/O      | ATAPI master / slave selection | 70      | CPUDT3    |     | System control data            |

| 24      | NINT0    | 0        | System control interruption 0  | 70      | VSS       |     | GND                            |

| 25      | NINT0    | 0        | System control interruption 0  | 72      | CPUDT2    |     | System control data            |

| 20      | WAITODC  | 0        | System control weight control  | 73      | CPUDT1    | I/O | System control data            |

| 28      | NMRST    | 0        | System control reset           | 74      | CPUDT0    | 1/O | System control data            |

| 20      | DASPST   |          | DASP signal initializing       | 74      | CLKOUT1   | 0   | 16.9/11.2/8.45MHz clock        |

|         |          | 1        |                                | 75      | VDD       | -   |                                |

| 30      | VDD      |          |                                |         |           |     | Apply 3V                       |

| 31      | OSCO2    | 1,0      | VSS connection,OPEN            | 77      | TEHLD     | 0   | Mirror gate                    |

| 32      | OSCI2    | I,O      | VSS connection, OPEN           | 78      | DTRO      | 0   | Data part frequency control    |

| 33      | UATASEL  | 1        | VSS connection                 | 70      | IDOT      | _   | switch                         |

| 34      | VSS      |          |                                | 79      | IDGT      | 0   | Part CAPA switch               |

| 35      | PVSSDRAM |          |                                | 80      | BDO       | I   | RF dropout / BCA data of       |

| 36      | PVDODRAM |          |                                | 04      |           |     | making to binary               |

| 37      | CPUADR17 |          | System control address         | 81      | CPDET2    |     | Outer side CAPA detection      |

| 38      | CPUADR18 |          | System control address         | 82      | CPDET1    |     | Side of surroundings on inside |

| 39      | VSS      | <u>.</u> |                                | 83      | VSS       |     | GND                            |

| 40      | CPUADR15 |          | System control address         | 84      | MMOD      |     | VSS connected                  |

| 41      | CPUADR14 |          | System control address         | 85      | NRST      |     | System reset                   |

| 42      | CPUADR13 |          | System control address         | 86      | VDD       | -   | Apply 3V                       |

| 43      | CPUADR12 |          | System control address         | 87      | CLKOUT2   | 0   | 16.9MHz clock                  |

| 44      | VDD      | _        | System control address         | 88      | PLLOK     | 0   | Frame mark detection           |

| 45      | CPUADR11 |          | System control address         | 89      | IDOHOLD   | 0   | ID gate for tracking holding   |

| 46      | CPUADR10 |          | System control address         | 90      | JMPINH    | 0   | Jump prohibition               |

| 47      | CPUADR9  |          | System control address         |         |           |     |                                |

| Pin NO. | Symbol  | I/O | Function                                      | Pin NO. | Symbol | I/O | Function                           |

|---------|---------|-----|-----------------------------------------------|---------|--------|-----|------------------------------------|

| 91      | LG      | 0   | Land / group switch                           | 133     | NPDIAG | I/O | ATAPI slave master diagnosis input |

| 92      | NTRON   | Ι   | Tracking ON                                   | 134     | VSS    |     |                                    |

| 93      | DACDATA | 0   | Cereal output                                 | 135     | DA1    | I/O | ATAPI host address                 |

| 94      | DACLRCK | 0   | L and R identification output                 | 136     | IOCS16 | 0   | ATAPI output of selection of width |

| 95      | DACCLK  | Ι   | Clock for cereal output                       |         |        |     | of host data bus                   |

| 96      | IPFLAG  | Ι   | Interpolation flag input                      | 137     | INTRQ  | 0   | ATAPI host interruption output     |

| 97      | BLKCK   | Ι   | Sub-code,Block clock input                    | 138     | 5VDD   |     |                                    |

| 98      | LRCK    | Ι   | L and R identification signal output          | 139     | NDMACK | Ι   | ATAPI host DMA response            |

| 99      | VSS     |     |                                               | 140     | IORDY  | 0   | ATAPI host ready output            |

| 100     | OSCI1   | I,O | 16.9MHz oscillation                           | 141     | NIORD  | Ι   | ATAPI host read                    |

| 101     | OSCO1   | I,O | 16.9MHz oscillation                           | 142     | VSS    |     |                                    |

| 102     | VDD     |     |                                               | 143     | NIOWR  | I/O | ATAPI host writes                  |

| 103     | PVSS    |     |                                               | 144     | DMARQ  | 0   | ATAPI host DMA demand              |

| 104     | PVDD    |     |                                               |         |        |     |                                    |

| 105     | P1      | I/O | Terminal MASTER polarity switch               |         |        |     |                                    |

|         |         |     | input                                         |         |        |     |                                    |

| 106     | P0      | I/O | CIRC-RAM OVER/UNDER                           |         |        |     |                                    |

|         |         |     | Interruption signal input                     |         |        |     |                                    |

| 107     | VSS     |     |                                               |         |        |     |                                    |

| 108     | SBCK    | 0   | Sub-code, Clock output for serial input       |         |        |     |                                    |

| 109     | SUBC    | Т   | Sub-code, Cereal input                        |         |        |     |                                    |

| 110     | XCLDCK  | Ι   | Sub-code, Frame clock input                   |         |        |     |                                    |

| 111     | CHCK4   | Ι   | Read clock to DAT3~0(Output of                |         |        |     |                                    |

|         |         |     | dividing frequency four from ADSC)            |         |        |     |                                    |

| 112     | DAT3    | Ι   | Read data from DISC                           |         |        |     |                                    |

| 113     | DAT2    | Ι   | (PAralle output from ADSC)                    |         |        |     |                                    |

| 114     | DAT1    | Ι   |                                               |         |        |     |                                    |

| 115     | DAT0    | Ι   |                                               |         |        |     |                                    |

| 116     | VDD     |     |                                               |         |        |     |                                    |

| 117     | SCLOCK  | I/O | Debugging cereal clock (270 $\Omega$ pull up) |         |        |     |                                    |

| 118     | SDATA   | I/O | Debugging cereal data (270 $\Omega$ pull up)  |         |        |     |                                    |

| 110~122 | MONI3~0 | 0   | Internal goods title monitor                  |         |        |     |                                    |

| 123     | VSS     | •   | Internal goods the monitor                    |         |        |     |                                    |

| 123     | NEJECT  | 1   | Eject detection                               |         |        |     |                                    |

| 125     | 5VDD    |     |                                               |         |        |     |                                    |

| 126     | NTRYCL  |     | Tray close detection                          |         |        |     |                                    |

| 127     | NDASP   | I/O | ATAPI Drive active/                           |         |        |     |                                    |

| ,       |         |     | Sulave connection I/O                         |         |        |     |                                    |

| 128     | NCS3FX  | 1   | ATAPI host chip selection                     |         |        |     |                                    |

| 129     | NCS1FX  |     | ATAPI host chip selection                     |         |        |     |                                    |

| 130     | VDD     | -   |                                               |         |        |     |                                    |

| 131     | DA2     | I/O | ATAPI host address                            |         |        |     |                                    |

|         | DA0     | 1/O | ATAPI host address                            |         |        |     |                                    |

| 132     |         |     |                                               |         |        |     |                                    |

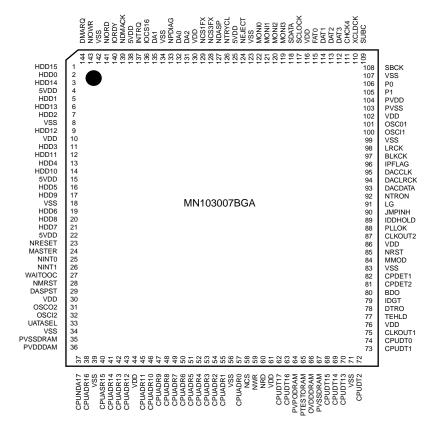

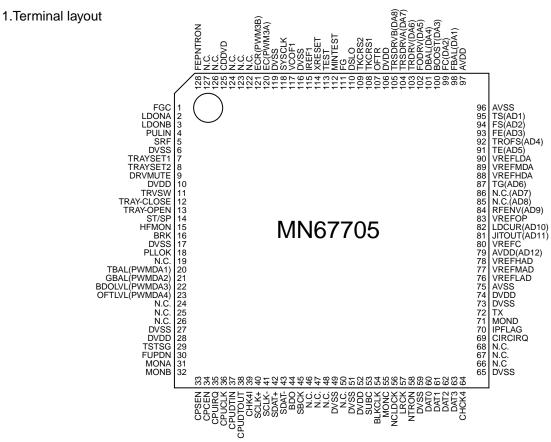

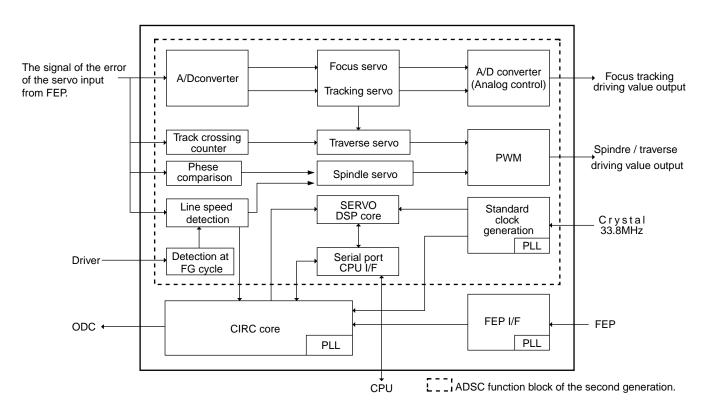

#### MN67705EA (IC201) : Digital servo controller

#### 2.Block diagram

3.Pin function

| <b>B</b> ' N | 0.1.1          | 1/0 | MN67705EA (1/3)                                          |

|--------------|----------------|-----|----------------------------------------------------------|

| Pin No.      | Symbol         | I/O | Function                                                 |

| 1            | FGC            | 0   | H fixation                                               |

| 2            | LDONA          | 0   | Laser drive controlA (ON / OFF)                          |

| 3            | LDONB          | 0   | Laser drive controlB (ON / OFF)                          |

| 4            | PULIN          | 0   | DSL and PLL high boost signal (FEP)                      |

| 5            | SRF            | 0   | Head amplifier gain H/L selection                        |

| 6            | DVSS           |     | Ground for digital circuit                               |

| 7            | TRAYSET1       | 0   | Tray drive ON/OFF and direction control                  |

| 8            | TRAYSET2       | 0   | Tray drive ON/OFF and direction control                  |

| 9            | DRVMUTE        | 0   | Drive IC mute control                                    |

| 10           | DVDD           | —   | Power supply for digital circuit                         |

| 11           | TRVSW          | I   | Surroundings position detection in traverse              |

| 12           | TRAY-CLOSE     | I   | Tray close detection SW                                  |

| 13           | TRAY-OPEN      | Ι   | Tray opening detection SW                                |

| 14           | ST/SP          | 0   | Spindle motor drive switch (START /STOP)                 |

| 15           | HFMON          | 0   | High cycle module control                                |

| 16           | BRK            | 0   | Spindle motor IC short brake control                     |

| 17           | DVSS           | —   | Ground for digital circuit                               |

| 18           | PLLOK          | I   | SYNC detection (DVD: 18T / CD: 22T)                      |

| 19           | N.C.           | 0   |                                                          |

| 20           | TBAL(PWMDA1)   | 0   | Tracking balance (FEP)                                   |

| 21           | GBAL(PWMDA2)   | 0   | Tangential balance (FEP)                                 |

| 22           | BDOLVL(PWMDA3) | 0   | BDO slice level (FEP)                                    |

| 23           | OFTLVL(PWMDA4) | 0   | Off-track error slice level (FEP)                        |

| 24           | N.C.           | 0   |                                                          |

| 25           | N.C.           | 0   |                                                          |

| 26           | N.C.           | 0   |                                                          |

| 27           | DVSS           | _   | Ground for digital circuit                               |

| 28           | DVDD           |     | Power supply for digital circuit                         |

| 29           | TSTSG          | 0   | Self calibration signal (FEP)                            |

| 30           | FUPDN          | 0   | Signal of frequency UP/DOWN of PLL (FEP)                 |

| 31           | MONA           | 0   | Monitor terminal A                                       |

| 32           | MONB           | 0   | Monitor terminal B                                       |

| 33           | CPSEN          | I   | Servo DSP cereal I/F chip selection (SYSCOM)             |

| 34           | CPCEN          | I   | CIRC cereal I/F chip selection (SYSCOM)                  |

| 35           | CPUIRQ         | 0   | Interrupt request to silicon (SYSCOM)                    |

| 36           | CPUCLK         |     | Silicon cereal I/F clock (SYSCOM)                        |

| 37           | CPUDTIN        | 1   | Silicon cereal I/F data input (SYSCOM)                   |

| 38           | CPUDTOUT       | 0   | Silicon cereal I/F data output (SYSCOM)                  |

| 39           | CHK4I          | 1   | Connects with unused DVSS                                |

| 40           | SCLK+          | 1   | Lead channel clock differential motion signal (positive) |

| 41           | SCLK-          | 1   | Lead channel clock differential motion signal (negative) |

| 42           | SDAT+          | 1   | Lead channel data differential motion signal (positive)  |

| 43           | SDAT-          | 1   | Lead channel data differential motion signal (negative)  |

| 44           | BDO            | 1   | BDO + BCA (FEP)                                          |

|              | SBCK           | 1   | CD sub-code data shift clock (ODC)                       |

| 45           |                |     |                                                          |

|         |                                       |       | MN67705EA (2/3)                                                |

|---------|---------------------------------------|-------|----------------------------------------------------------------|

| Pin No. | Symbol                                | I/O   | Function                                                       |

| 47      | IREF3                                 | _     | Connects with unused DVSS                                      |

| 48      | VCOF2                                 | _     | Connects with unused DVSS                                      |

| 49      | DVSS                                  | —     | Ground for digital circuit                                     |

| 50      | VCOE3                                 | _     | Connects with unused DVSS                                      |

| 51      | DVSS                                  | —     | Ground for digital cirucuit                                    |

| 52      | DVDD                                  | _     | Power supply for digital cirucuit                              |

| 53      | SUBC                                  | 0     | CD sub-code (ODC)                                              |

| 54      | BLKCLK                                | 0     | CD sub-code synchronous signal (ODC)/Jump output of one at DVD |

| 55      | MONC                                  | 0     | Monitor terminal C                                             |

| 56      | NCLDCK                                | 0     | Sub-code data freme clock (ODC)                                |

| 57      | LRCK                                  | 0     | LR channnel data strove circCIRC(ODC)                          |

| 58      | NTRON                                 | 0     | L: Tracking ON (ODC)                                           |

| 59      | DVSS                                  |       | Ground for digital cirucuit                                    |

| 60      | DAT0                                  | 0     | CIRC / Binary making DVD data output                           |

| 61      | DAT1                                  | 0     | CIRC / Binary making DVD data output                           |

| 62      | DAT2                                  | 0     | CIRC / Binary making DVD data output                           |

| 63      | DAT3                                  | 0     | CIRC / Binary making DVD data output                           |

| 64      | CHCK4                                 | 0     | Synchronous clock of DAT0~3                                    |

| 65      | DVSS                                  | _     | Ground for digital circuit                                     |

| 66      | DACCLK                                | 0     |                                                                |

| 67      | DACLRCK                               | 1     | Connects with unused DVSS                                      |

| 68      | DACDATA                               |       | Connects with unused DVSS                                      |

| 69      | CIRCIRQ                               | 0     | RAM with built-in CIRC exceeds / Underflow interrupt           |

| 70      | IPFLAG                                | 0     | CIRC error flag                                                |

| 71      | MOND                                  | 0     | Monitor terminal D                                             |

| 72      | TX                                    | 0     | Digital audio interface                                        |

| 73      | DVSS                                  |       | Ground for digital cirucuit                                    |

| 74      | DVDD                                  |       | Power supply for digital cirucuit                              |

| 75      | AVSS                                  | _     | Ground for analog cirucuit                                     |

| 76      | VREFLAD                               |       | AD subordinate position standard voltage $(0.6 \pm 0.1v)$      |

| 77      | VREFMAD                               |       | It is a place standard voltage in AD $(1.4\pm0.1V)$            |

| 78      | VREFHAD                               |       | High-ranking AD standard voltage ( $2.2 \pm 0.1V$ )            |

| 79      | AVDD                                  |       | Power supply for analog circuit                                |

| 80      | VREFC(AD12)                           | I     |                                                                |

| 81      | JIOUT(AD11)                           |       | Jitter signal(FEP)                                             |

| 82      | LDCUR(AD10)                           |       | Laser drive current signal                                     |

| 83      | VREFOP                                | · _   | Operation amplifier standard voltage(VREFC)                    |

| 84      | RFENV(AD9)                            | 1     | RFENV(FEP)                                                     |

| 85      | N.C.(AD8)                             | <br>- | Connects with VREFC                                            |

| 86      | N.C.(AD7)                             |       | Connects with VREFC                                            |

| 87      | TG(AD6)                               | I     | Tangential Phase difference (FEP)                              |

| 88      | VREFHDA                               | · _   | High-ranking AD standard voltage ( $2.2 \pm 0.1V$ )            |

| 89      | VREFMDA                               |       | It is a place standard voltage in AD $(1.4\pm0.1V)$            |

| 90      | VREFLDA                               |       | AD subordinate position standard voltage $(0.6 \pm 0.1v)$      |

| 91      | TE(AD5)                               | 1     | Tracking error (FEP)                                           |

| 92      | TROFS(AD4)                            |       | Tracking drive IC input offset                                 |

| 93      | FE(AD3)                               |       | Focus error (FEP)                                              |

|         | (,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | L '   |                                                                |

| -       |              |     | MN67705EA(3/3)                             |

|---------|--------------|-----|--------------------------------------------|

| Pin No. | Symbol       | I/O | Function                                   |

| 94      | FS(AD2)      | I   | FS (FEP)                                   |

| 95      | TS(AD1)      | Ι   | TS (FEP)                                   |

| 96      | AVSS         |     | Ground for analog cirucuit                 |

| 97      | AVDD         |     | Power supply for analog circuit            |

| 98      | FBAL(DA1)    | 0   | Focus balance(FEP)                         |

| 99      | FC(DA2)      | 0   | Cutting off frequency (FEP)                |

| 100     | BOOST(DA3)   | 0   | Amount of boost (FEP)                      |

| 101     | TBAL(DA4)    | 0   | DSL offset balance (FEP)                   |

| 102     | FODRV(DA5)   | 0   | Focus drive                                |

| 103     | TRDRV(DA6)   | 0   | Tracking drive                             |

| 104     | TRSDRVA(DA7) | 0   | Traverse drive A aspect                    |

| 105     | TRSDRVB(DA8) | 0   | Traverse drive B aspect                    |

| 106     | DVDD         | —   | Power supply for digital cirucuit          |

| 107     | OFTR         | I   | Off-track error signal (FEP)               |

| 108     | TKCRS1       | I   | Track crossing signal 1 (FEP)              |

| 109     | TKCRS2       | I   | Track crossing signal 2 (FEP)              |

| 110     | DSLO         | I   | Binary making data slice signal (FEP)      |

| 111     | FG           | I   | FG signal input (spindle motor driver)     |

| 112     | MINTEST      |     | Connects with DVSS                         |

| 113     | TEST         |     | Connects with DVSS                         |

| 114     | XRESET       | Ι   | Reset L: Reset                             |

| 115     | IREF1        |     | VCO reference current 1( for SYSCLK)       |

| 116     | DVSS         |     | Ground for digital circuit)                |

| 117     | VCOF1        | —   | VCO control voltage 1 (for SYSCLK)         |

| 118     | SYSCLK       | I   | 33.8MHz system clock input                 |

| 119     | DVSS         |     | Ground for digital circuit                 |

| 120     | EC(PWM3A)    | 0   | Spindle motor drive                        |

| 121     | ECR(PWM3B)   | 0   |                                            |

| 122     | N.C.(PWM3A)  | 0   |                                            |

| 123     | N.C.(PWM2B)  | 0   |                                            |

| 124     | N.C.(PWM1A)  | 0   |                                            |

| 125     | CDDVD        | 0   | CD/DVD control signal (FEP) CD : H DVD : L |

| 126     | N.C.(PWM0A)  | 0   |                                            |

| 127     | N.C.(PWM0B)  | 0   |                                            |

| 128     | FEPNTRON     | 0   | Tracking ON (FEP)                          |

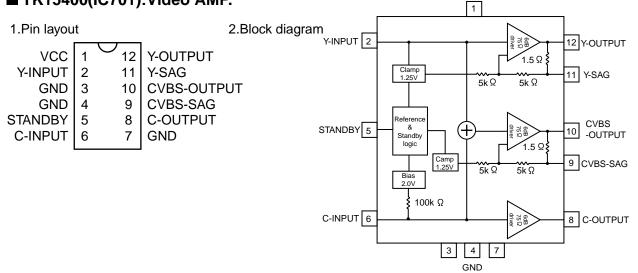

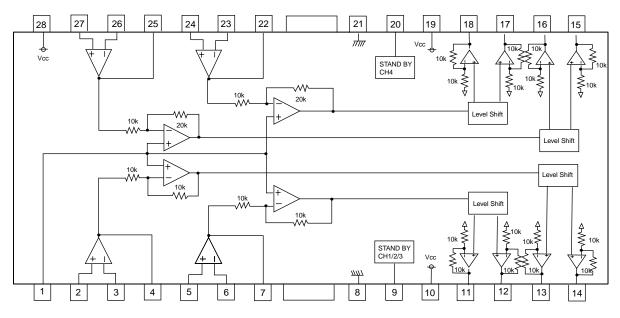

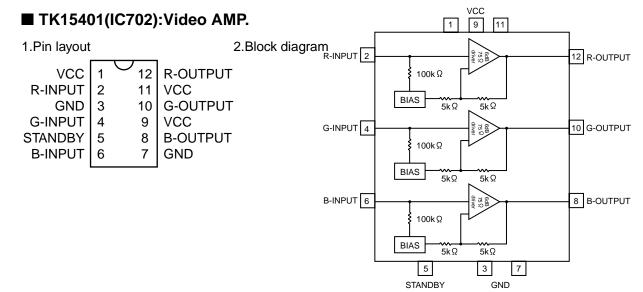

#### TK15400(IC701):Video AMP.

VCC

#### XV-D721BK XV-D723GD ■ BA5983FM-X(IC271):4CH driver

#### 1. Block diagram

#### 2. Pin function

| Pin No. | Symbol   | I/O | Function                | Pin No. | Symbol   | 1/0 | Function                |

|---------|----------|-----|-------------------------|---------|----------|-----|-------------------------|

| 1       | BLAS IN  | I   | Amplifier input         | 15      | VO4(+)   | 0   | CH4 output (+)          |

| 2       | OPIN1(+) | I   | CH1 amplifier input (+) | 16      | VO4(-)   | 0   | CH4 output (-)          |

| 3       | OPIN1(-) | I   | CH1 amplifier input (-) | 17      | VO3(+)   | 0   | CH3 output (+)          |

| 4       | OPOUT1   | 0   | CH1 amplifier output    | 18      | VO3(-)   | 0   | CH3 output (-)          |

| 5       | OPIN2(+) | I   | CH2 amplifier input (+) | 19      | PowVcc2  | -   | CH3/4 power supply      |

| 6       | OPIN2(-) | I   | CH2 amplifier input (-) | 20      | STBY2    | I   | CH4 input               |

| 7       | OPOUT2   | 0   | CH2 amplifier output    | 21      | GND      | -   | Ground                  |

| 8       | GND      | -   | Ground                  | 22      | OPOUT3   | 0   | CH3 amplifier output    |

| 9       | STBY1    | I   | CH1/2/3 input control   | 23      | OPIN3(-) | I   | CH3 amplifier input (-) |

| 10      | PowVcc1  | -   | CH1/2 power supply      | 24      | OPIN3(+) | I   | CH3 amplifier input (+) |

| 11      | VO2(-)   | 0   | CH2 output (-)          | 25      | OPOUT4   | 0   | CH4 amplifier output    |

| 12      | VO2(+)   | 0   | CH2 output (+)          | 26      | OPIN4(-) | I   | CH4 amplifier input (-) |

| 13      | VO1(-)   | 0   | CH1 output (-)          | 27      | OPIN4(+) |     | CH4 amplifier input (+) |

| 14      | VO1(+)   | 0   | CH1 output (+)          | 28      | PreVcc   | -   | Power supply pin        |

## MN101C23DBP3 (IC810) : System controller

| Pin No.     | Symbol   | I/O | Descriptions                                                            |

|-------------|----------|-----|-------------------------------------------------------------------------|

| 1           | KCMND    | 0   | VC3 Serial data output                                                  |

| 2           | MSTAT    |     | VC3 Status data input                                                   |

| 3           | KCLK     | I   | VC3 Serial clock input                                                  |

| 4           | DATAOUT  | 0   | SLC/TUNER data output                                                   |

| 5           | DATAIN   | l i | SLC/TUNER data input                                                    |

| 6           | CK       | 0   | SLC/TUNER clock signal output                                           |

| 7           | BEAT     | 0   | BEAT Cut signal output of TUNER                                         |

| 8           | VDD      | -   | Power supply +5V                                                        |

| 9,10        | OSC2,1   | I/O | Oscillation terminal (8MHz)                                             |

| 11          | VSS      | -   | Connect to GND                                                          |

| 12,13       | XI,XO    | I/O | Sub clock (32.768kHz)                                                   |

| 14          | MMOD     | -   | Connect to GND                                                          |